Intel présente ses travaux de recherche pour intégrer davantage de puissance de calcul dans les puces au-delà de 2025

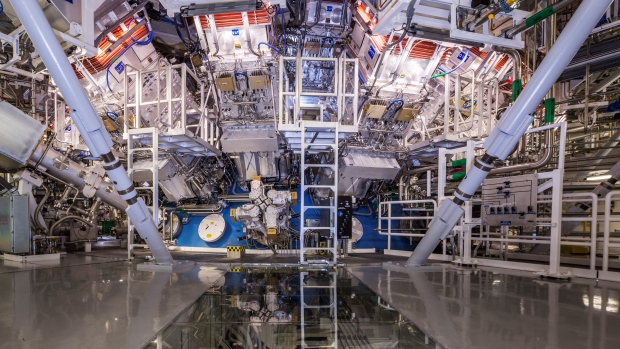

Les équipes de recherche d’Intel Corp. ont dévoilé samedi des travaux qui, selon la société, l’aideront à accélérer et à réduire la taille des puces informatiques au cours des dix prochaines années, avec plusieurs technologies visant à empiler les parties des puces les unes sur les autres.

Le groupe de recherche sur les composants d’Intel a présenté ces travaux dans des documents lors d’une conférence internationale qui se tient à San Francisco. L’entreprise de la Silicon Valley s’efforce de reprendre l’avantage dans la fabrication des puces les plus petites et les plus rapides qu’elle a perdu ces dernières années au profit de rivaux tels que Taiwan Semiconductor Manufacturing Co et Samsung Electronics Co Ltd.

Alors que le PDG d’Intel, Pat Gelsinger, a présenté des plans commerciaux visant à regagner cette avance d’ici 2025, les travaux de recherche dévoilés samedi donnent un aperçu de la manière dont Intel prévoit d’affronter la concurrence au-delà de 2025.

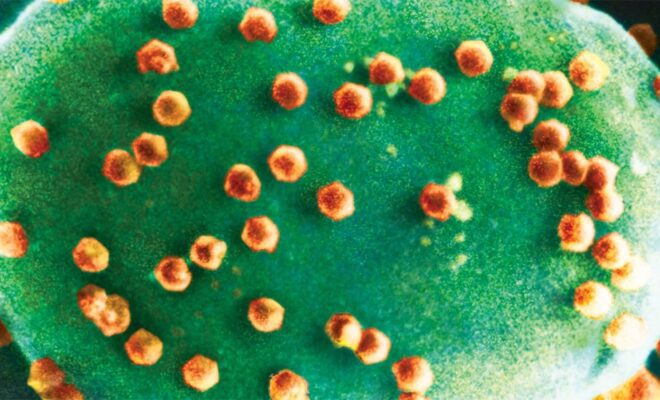

L’une des façons dont Intel intègre davantage de puissance de calcul dans ses puces consiste à empiler des « tuiles » ou des « chiplets » en trois dimensions plutôt que de fabriquer des puces en une seule pièce bidimensionnelle. Intel a présenté samedi un travail qui pourrait permettre de multiplier par dix les connexions entre les tuiles empilées, ce qui signifie que des tuiles plus complexes peuvent être empilées les unes sur les autres.

Mais la plus grande avancée présentée samedi est sans doute un document de recherche démontrant un moyen d’empiler les transistors – de minuscules interrupteurs qui constituent les éléments de base des puces en représentant les 1 et les 0 de la logique numérique – les uns sur les autres.

Intel pense que cette technologie permettra d’augmenter de 30 à 50 % le nombre de transistors qu’il est possible de placer dans une zone donnée d’une puce. L’augmentation du nombre de transistors est la principale raison pour laquelle les puces sont devenues de plus en plus rapides au cours des 50 dernières années.

« En empilant les dispositifs directement les uns sur les autres, nous économisons clairement de la surface », a déclaré à Reuters Paul Fischer, directeur et ingénieur principal du groupe de recherche sur les composants d’Intel, lors d’une interview. « Nous réduisons les longueurs d’interconnexion et économisons réellement de l’énergie, ce qui rend ce système non seulement plus rentable, mais aussi plus performant. »

(Reportage de Stephen Nellis à San Francisco ; édition de Nick Zieminski)